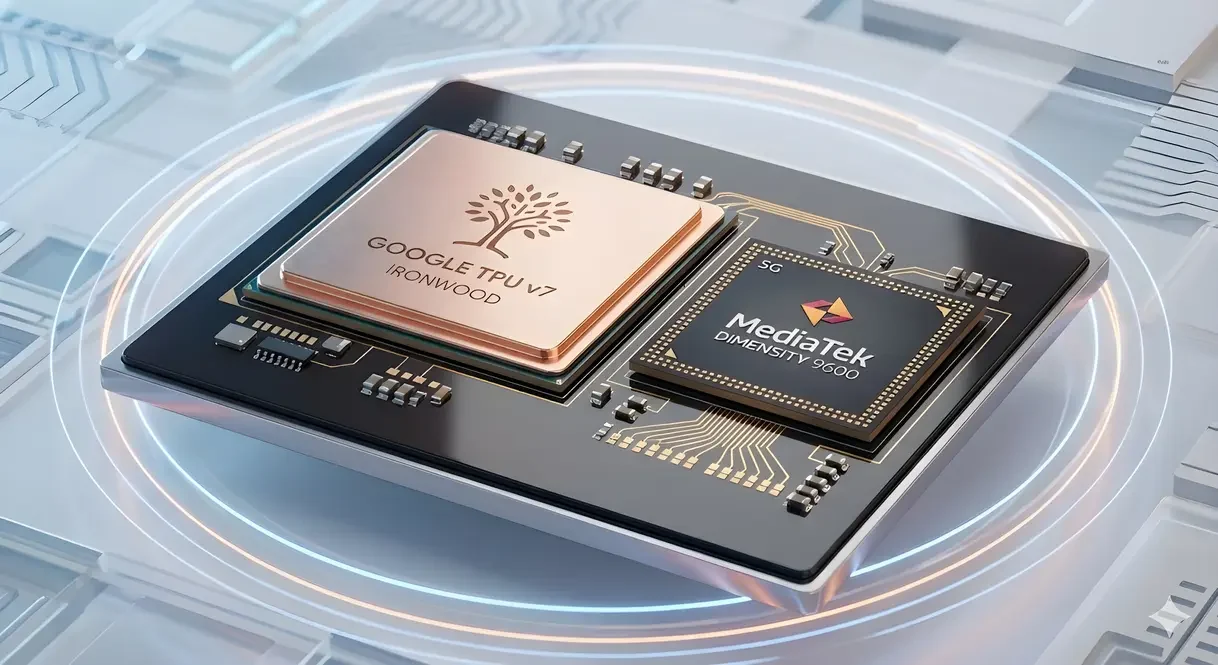

Новый TPU Ironwood v7 от Google стал первым жизнеспособным ASIC, способным соперничать с GPU Blackwell от NVIDIA. Это событие привлекло широкий интерес к процессу разработки TPU в Google и к его партнёрам, среди которых тайваньская MediaTek, готовая превратить полученный опыт в реальное повышение эффективности своих кастомных чипов, начиная с анонсированного SoC Dimensity 9600.

TPU Ironwood v7 от Google и роль MediaTek в проекте

Прежде чем перейти к Dimensity 9600 от MediaTek, разберём, о чём именно идёт речь в обсуждениях вокруг Google Ironwood TPU v7. Вот всё, что известно об архитектуре новых TPU на данный момент:

- Дизайн с двумя чиплетами, каждый из которых содержит:

- 1× TensorCore с систолической матричной архитектурой, обеспечивающий чрезвычайно эффективные операции умножения матриц — ядро большинства AI‑нагрузок, включая обучение и инференс нейронных сетей — за счёт значительного снижения количества чтений и записей в HBM.

- Векторный процессор (VPU) отвечает за общие по‑элементные операции, необходимые моделям ИИ, такие как функции активации (например, ReLU) и нормализации.

- Блок умножения матриц (MXU) осуществляет сами операции матричного умножения.

- 2× SparseCores, оптимально обрабатывающие сценарии с нерегулярным, зависящим от данных доступом к памяти, включая работу с огромными математическими структурами‑встраиваниями, которые превращают огромные категориальные признаки (например, список словарных токенов) в компактные плотные векторы — ключевой шаг в большинстве AI‑операций.

- 96 ГБ памяти с высокой пропускной способностью (HBM).

- 1× TensorCore с систолической матричной архитектурой, обеспечивающий чрезвычайно эффективные операции умножения матриц — ядро большинства AI‑нагрузок, включая обучение и инференс нейронных сетей — за счёт значительного снижения количества чтений и записей в HBM.

- Два чиплета соединены через межчиповый (D2D) интерфейс, в 6 раз быстрее, чем обычный 1‑мерный (ICI) канал.

- Один стенд TPU включает 64 чипа, связанных ICI, каждый из которых получает 1,2 ТБ/с двунаправленной пропускной способности ICI. Эту базовую конфигурацию из 64 чипов называют «кубом».

- Несколько кубов объединяются через оптический коммутатор (OCS) в суперпод, состоящий из 9 216 чипов и 144 кубов.

Что касается производительности нового TPU от Google, достаточно взглянуть на указанные выше цифры. Как мы отмечали в отдельной статье, TPU v7 Ironwood демонстрирует серьёзную конкуренцию GPU NVIDIA в задачах инференса, которые становятся всё более значимыми по мере того, как индустрия отходит от огромных фундаментальных AI‑моделей. Фактически, анонсируемый TPU обладает ниже общей стоимости владения (TCO) при почти сопоставимой производительности с новейшими графическими процессорами NVIDIA.

Роль MediaTek в TPU Ironwood v7 от Google

MediaTek сыграла важную роль в проектировании TPU Ironwood v7, и теперь готова использовать полученные выводы для повышения эффективности будущего чипа Dimensity 9600.

Согласно сообщениям, появившимся в марте 2025 года, Google поручила MediaTek разработать ввод‑вывод (I/O) модули Ironwood, обеспечивающие связь процессора с периферией. Это отход от прежней стратегии Google, когда последующее поколение TPU разрабатывалось в тесном сотрудничестве с Broadcom.

По оценке UBS, MediaTek может заработать около 4 млрд долларов благодаря сотрудничеству с Google над новым TPU.

Как работа MediaTek над TPU Ironwood v7 улучшает перспективы более эффективного Dimensity 9600

Стоит помнить, что ASIC и мобильные процессоры (AP) вроде Dimensity 9600 по своей природе различны. Это значит, что MediaTek не сможет полностью перенести весь опыт в Dimensity 9600, однако компания способна реализовать ряд итеративных улучшений:

- Разработать более эффективную стратегию отключения питания (power gating) для Dimensity 9600, позволяющую более агрессивно отключать отдельные I/O‑блоки при их неиспользовании.

- Улучшить масштабирование напряжения, позволяя процессору работать при оптимальном уровне напряжения и тем самым снизить энергопотребление.

- Отточить существующие схемы отключения тактовой частоты (clock gating), повышая время работы от батареи и облегчая соблюдение строгих энергетических бюджетов.

Конечно, MediaTek также разрабатывает собственные AI‑чипы, где её опыт работы с TPU будет особенно актуален. Тем не менее, её мобильные процессоры могут извлечь выгоду из перечисленных доработок. Это особенно важно, учитывая, что MediaTek уже отказалась от «ядер эффективности» в архитектуре своих мобильных процессоров.

Автор – wccftech.com