В новой исследовательской работе компания AMD изучает способы укладки (стекирования) кэш-памяти L2 в своих будущих чипах, что позволит добиться схожей или даже лучшей задержки.

3D V-Cache, но для L2: AMD исследует интеграцию стекированных кэшей L2 помимо L3 в будущих чипах

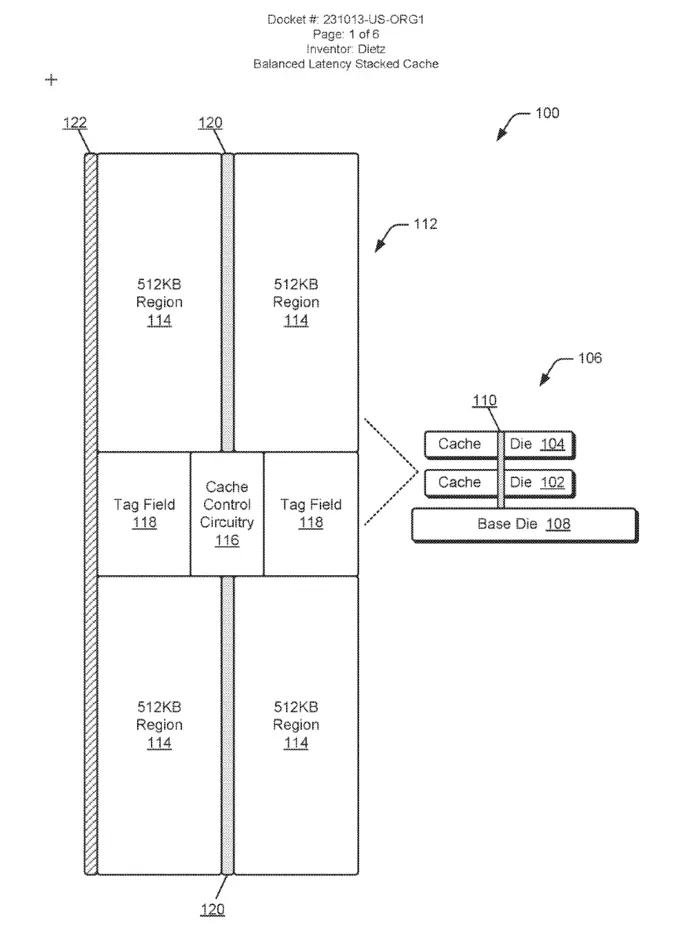

AMD опубликовала интересную научную статью под названием «Сбалансированный по задержке стекированный кэш» (Balanced Latency Stacked Cache) с номером патентной заявки «US20260003794A1». В этой работе AMD раскрывает методики создания сбалансированного по задержке стекированного кэша, где система кэширования включает первый кристалл кэша и как минимум второй кристалл кэша, расположенный в стеке поверх первого.

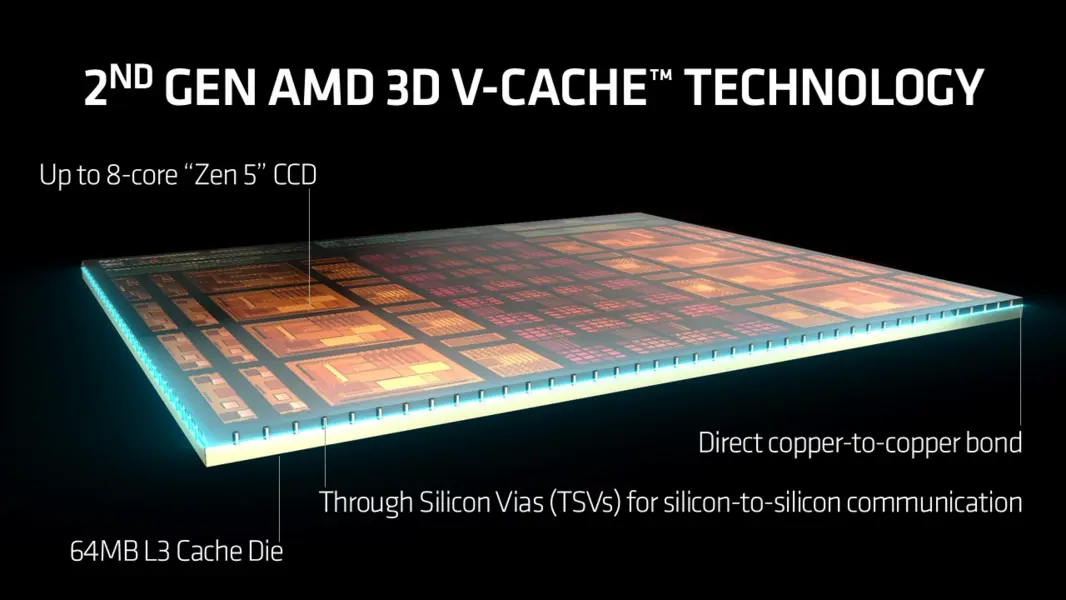

Нам уже известно, что AMD предлагает стекированный кэш в виде технологии 3D V-Cache, которая использует дополнительный слой кэш-памяти L3, расположенный либо поверх чиплетов с вычислительными ядрами, либо под ними. Первое поколение 3D V-Cache было размещено поверх чиплетов Zen, в то время как во втором поколении стек переместился под вычислительный чиплет. По сути, эти подходы схожи, поскольку оба используют слой стекированного кэша.

Технология 3D V-Cache от AMD используется в чипах от клиентской линейки «Ryzen» до мощнейших серверных решений, таких как линейка «EPYC». Пока AMD продолжает совершенствовать свои технологии L3 3D V-Cache, компания ищет новые пути для стекирования других типов кэша. Патент указывает на то, что следующим шагом команды в красном станет стекирование L2.

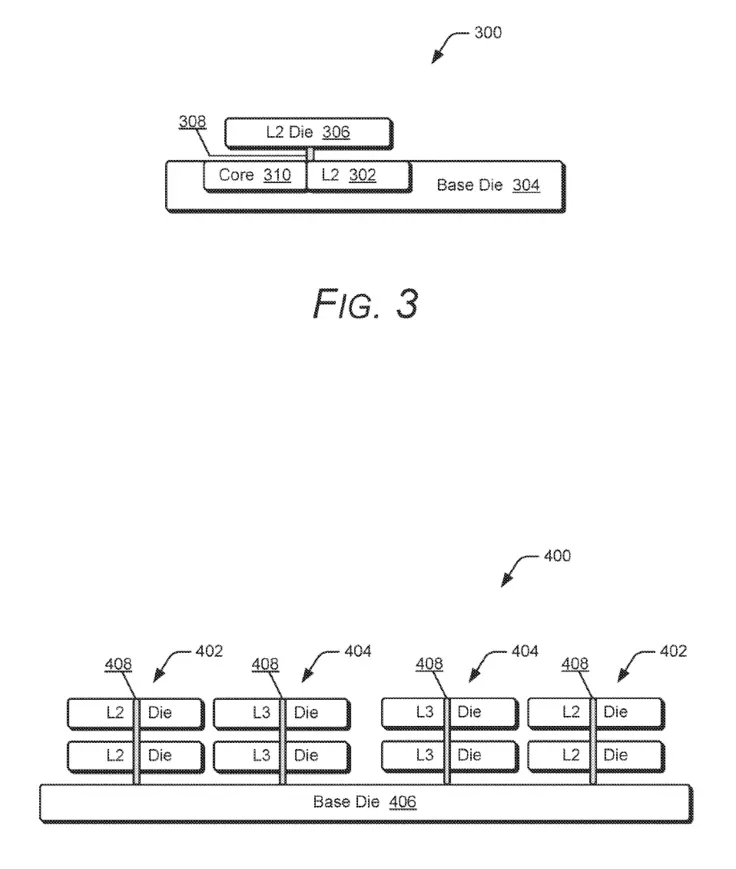

Для своего дизайна стекированного кэша L2 AMD использует наглядный пример, демонстрирующий базовый кристалл, соединенный с вычислительным кристаллом и кристаллом кэша, а затем поверх них добавляется еще один вычислительный кристалл и кристалл кэша. В этом примере используется кэш-модуль с четырьмя областями по 512 КБ, что дает суммарно 2 МБ кэша L2, и схемы управления кэшем (CCC). Этот комплекс L2 может быть расширен до 4 МБ, как показано на блок-схеме.

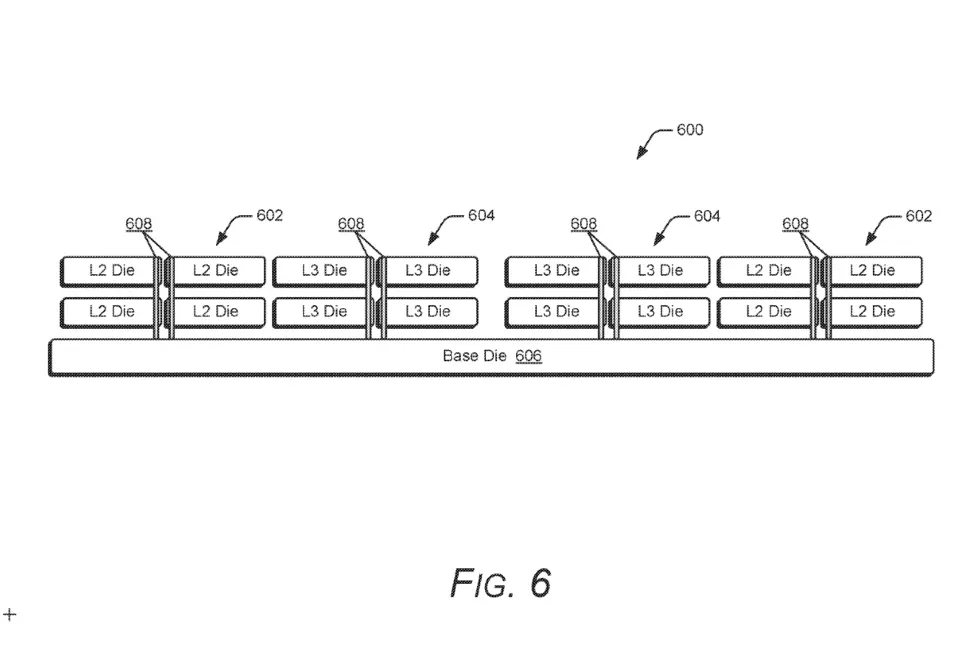

Подход к стекированию использует тот же принцип 3D V-Cache: стеки L2/L3 крепятся к базовому кристаллу и вычислительным комплексам с использованием кремниевых переходных отверстий (Silicon Vias), расположенных вертикально в центре стекированной кэш-системы, которая состоит из первого и второго кристаллов кэша. CCC управляет вводом и выводом данных.

В статье AMD приводит примеры конфигураций планарного кэша L2 объемом 1 МБ и 2 МБ. Указывается, что планарный кэш L2M объемом 1 МБ имеет типичную задержку в 14 тактов, тогда как стекированный L2M объемом 1 МБ демонстрирует задержку всего в 12 тактов. Это доказывает, что стекированный кэш L2 может не только обеспечивать большую емкость, но и достигать сопоставимой или лучшей циклической задержки по сравнению с традиционными планарными решениями.

В аспектах описанных техник конфигурация стекированной кэш-системы снижает задержку отклика при доступе к стекированному кэшу, а также обеспечивает функцию энергосбережения. Стекированная кэш-система улучшает производительность передачи данных и имеет меньшую задержку, чем обычный планарный кэш, реализованный на одном кристалле. Примечательно, что соединительные переходные отверстия проложены внутрь и наружу из центра стекированной кэш-системы. Это позволяет избежать добавления каскадов (также именуемых конвейерными каскадами), как в традиционном планарном кэше, для маршрутизации данных по одной части кэша, чтобы достичь части кэша, которая находится дальше от вводов/выводов данных.

В описанных техниках соединительные переходные отверстия, проложенные по центру стекированной кэш-системы, создают сбалансированные (или идентичные) задержки между двумя половинами стекированной кэш-системы на стекированном кристалле (например, первого и как минимум второго кристалла кэша). Например, традиционный планарный кэш L2M объемом 1 МБ имеет задержку в 14 тактов, в то время как стекированный кэш L2M объемом 1 МБ, реализованный с использованием описанных техник, имеет задержку всего в 12 тактов. Это позволяет реализовать более крупный стекированный кэш, чем традиционный планарный, при этом достигая такой же или лучшей циклической задержки.

Соответственно, описанные аспекты сбалансированного по задержке стекированного кэша обеспечивают меньшую задержку для запроса доступа, и данные возвращаются из кэша быстрее. Также происходит экономия энергии, поскольку запрос на доступ выполняется за меньшее количество циклов, и кэш L2, например, остается включенным не так долго, а также экономия энергии при более быстром переходе из активного состояния в режим ожидания кэша. Кроме того, длины проводников в кристалле кэша короче, что фактически приводит к снижению емкости и также экономит энергию. Также снижается нагрузка на сигнал, поскольку сигналы проходят только половину расстояния для запроса доступа и возврата данных. Более того, генерируется меньше тепла в результате экономии энергии, меньшей емкости и прохождения сигналов на меньшее расстояние.

И дело не только в лучшей задержке: AMD также сообщает, что стекированный кэш L2 обеспечивает и экономию энергии. Пройдет некоторое время, прежде чем мы увидим стекированные кэши L2 в действии на реальных чипах, но, как и в случае со стекированным L3 3D V-Cache, есть веские основания полагать, что эта технология будет интегрирована в будущие чипы AMD, будь то процессоры или графические ускорители. Время покажет.

Всегда имейте в виду, что редакции могут придерживаться предвзятых взглядов в освещении новостей.

Автор – Hassan Mujtaba