Процессоры Intel Xeon Diamond Rapids следующего поколения будут включать два новых отдельных модуля под кодовыми названиями CBB и IMH.

Процессоры Intel Xeon Diamond Rapids получат вычислительный модуль CBB и модуль ввода/вывода IMH с поддержкой PCIe Gen6

В патчах ядра Linux обнаружены новые подробности о процессорах Intel Xeon Diamond Rapids следующего поколения. Эти патчи раскрывают философию дизайна будущей архитектуры Xeon и то, как будут изготавливаться чипы.

В Diamond Rapids Intel представит два совершенно новых модуля. Во-первых, это CBB (Core Building Block) — вычислительный модуль. Главная особенность заключается в том, что, в отличие от Granite Rapids, где IMC (контроллер памяти) был добавлен на тот же модуль, в Diamond Rapids он будет отдельным.

IMC, или интегрированный контроллер памяти, будет размещен на новом модуле IMH (Integrated I/O & Memory Hub) — интегрированном хабе ввода/вывода и памяти. Они отделены от вычислительного модуля (CBB), и Diamond Rapids, как утверждается, будет иметь до двух таких IMH-чипов. Также, по словам @InstLatX64, IMH-чип будет расположен на базовом модуле, как это реализовано в Clearwater Forest.

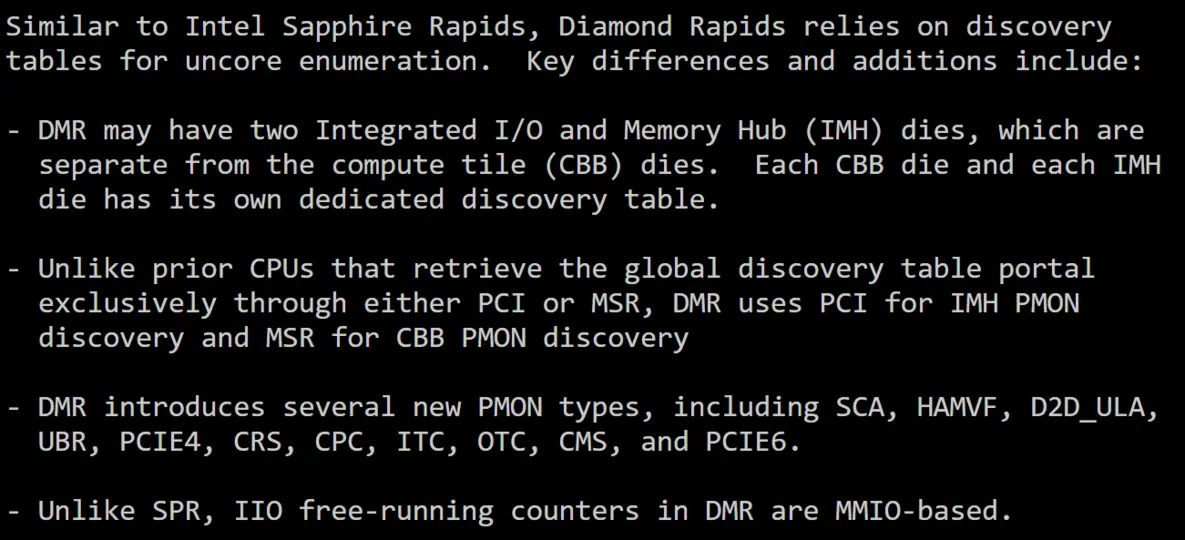

Как и Intel Sapphire Rapids, Diamond Rapids использует таблицы обнаружения для перечисления не-ядерных компонентов. Ключевые отличия и дополнения включают:

- DMR может иметь два чипа Integrated I/O and Memory Hub (IMH), которые отделены от вычислительных чипов (CBB). Каждый чип CBB и каждый чип IMH имеет свою собственную таблицу обнаружения.

- В отличие от предыдущих процессоров, которые извлекают глобальный портал таблицы обнаружения исключительно через PCI или MSR, DMR использует PCI для обнаружения IMH PMON и MSR для обнаружения CBB PMON.

- DMR представляет несколько новых типов PMON, включая SCA, HAMVF, D2D_ULA, UBR, PCIE4, CRS, CPC, ITC, OTC, CMS и PCIE6.

- В отличие от SPR, свободно работающие счетчики IIO в DMR основаны на MMIO.

Помимо этого, упоминаются и другие детали, такие как поддержка PCIe Gen6, что вполне логично, поскольку технология была анонсирована еще в 2026 году и в этом году появится на платформах ЦП для центров обработки данных следующего поколения, таких как Diamond Rapids и Venice.

Согласно предыдущей информации, процессоры Intel Xeon Diamond Rapids будут иметь до 192 ядер, а некоторые слухи даже указывают на 256 ядер, хотя Intel пока не подтвердила многие детали. Известно, что в чипах будет использоваться новейший техпроцесс 18A, а архитектура ядра будет Panther Cove P-Cores. Ранние детали платформы указывают на TDP до 650 Вт на платформе LGA 9324 с возможностью использования нескольких сокетов. Ожидается, что Intel представит свои процессоры Diamond Rapids к середине или второй половине 2026 года.

Всегда имейте в виду, что редакции некоторых изданий могут придерживаться предвзятых взглядов в освещении новостей.

7/9

Автор – Hassan Mujtaba