Ещё в начале 2021 года появились первые слухи и намёки на новую технологию кэш-памяти, над которой работала компания AMD. Официально она была представлена позднее, в середине года на выставке Computex и получила название 3D V-cache. По сути, это вертикально уложенный кэш последнего уровня (LLC), который позволяет компании разместить большой объём памяти на минимальной площади.

В настоящее время AMD использует второе поколение технологии 3D V-cache, и недавно на выставке CES был представлен процессор Ryzen 7 9850X3D, который компания назвала самым быстрым игровым процессором в мире.

В архитектуре Zen от AMD кэш последнего уровня (LLC) соответствует третьему уровню (L3). Однако похоже, что компания намерена внести изменения в свою иерархию кэша: недавний патент свидетельствует о том, что AMD теперь работает над вертикальным размещением и кэша второго уровня (L2) для достижения ещё большей производительности и/или энергоэффективности.

Компания подала заявку на патент, который она называет «Кэш с балансировкой задержек при укладке» (Balanced Latency Stacked Cache). Эта конструкция призвана снизить задержки при доступе к кэш-памяти и ещё больше повысить энергоэффективность в будущих процессорах Ryzen X3D.

По сравнению с процессорами с 3D V-cache, традиционные планарные процессоры с кэшем без вертикальной укладки имеют более высокие задержки и энергозатраты. Это, соответственно, ведёт к снижению производительности и эффективности. Учитывая эти преимущества, новая конструкция кэша L2 с 3D-технологией от AMD обещает сократить количество тактов, необходимых для доступа к типичному 1 МБ кэша L2, с 14 до всего лишь 12 тактов.

Хотя это может показаться незначительным изменением, в разработке архитектуры ЦП это повод для большого энтузиазма, поскольку даже такое небольшое сокращение имеет огромное значение для общей конечной производительности и эффективности. Для справки: типичный кэш L2 требует 10–50 тактов, так что это определённо один из лучших показателей.

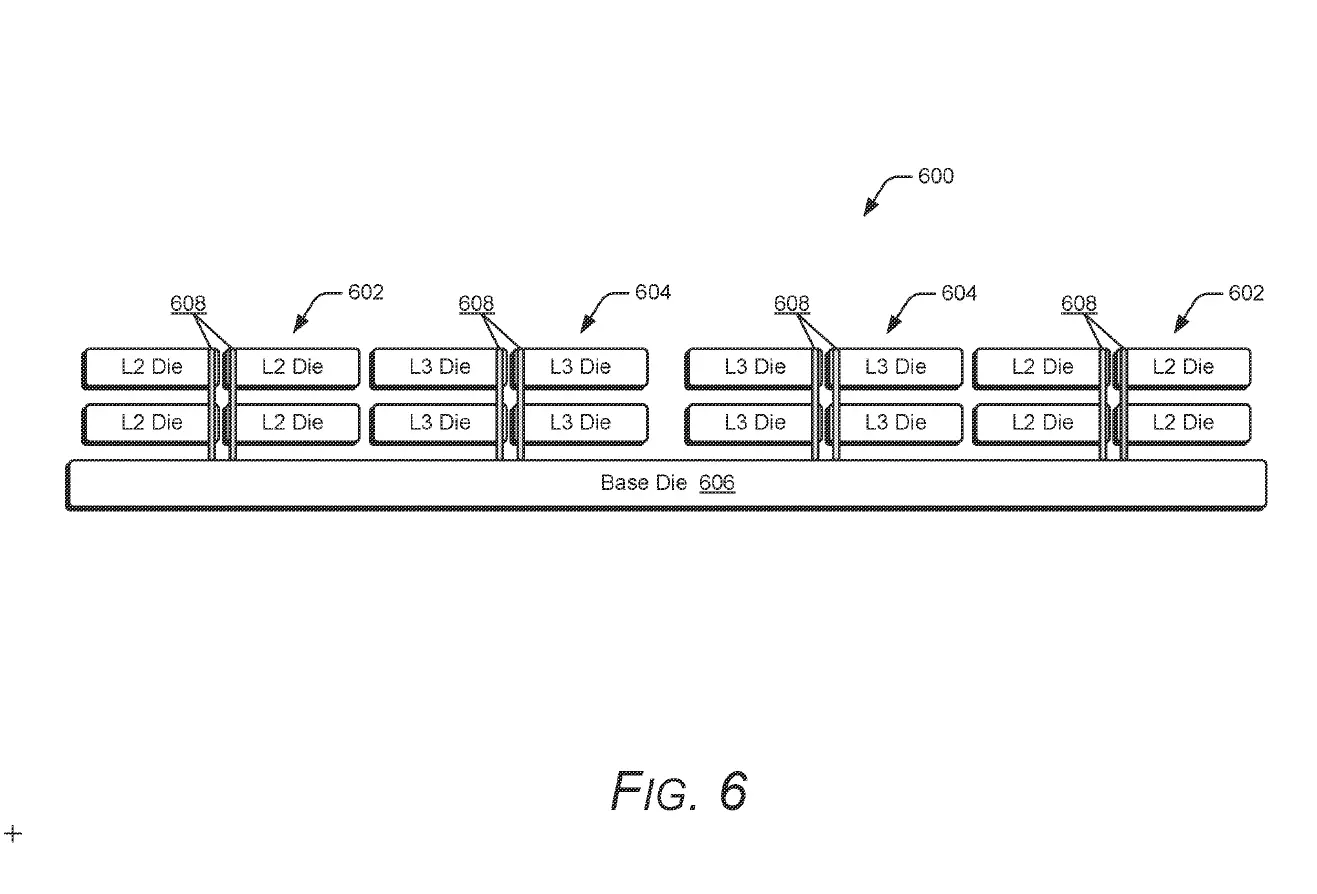

Если вам интересно, как AMD это реализует, в патенте отмечается, что уложенные кристаллы соединяются посредством соединительных переходных отверстий, таких как сквозные кремниевые переходные отверстия (TSV) или переходные отверстия контактных площадок (BPV) для вертикальной кремний-кремниевой связи. Эти соединительные отверстия прокладываются через центр, тем самым сокращая длину проводников или этапов конвейера. Более того, прокладывая соединения через центр уложенных кристаллов, AMD создаёт симметричную или сбалансированную структуру, что должно обеспечить равномерность времени доступа к данным во всех слоях. Именно поэтому патент и называется «Кэш с балансировкой задержек при укладке» (Balanced Latency Stacked cache).

Патент пока находится на рассмотрении, поэтому остаётся только ждать, что произойдёт дальше. Конечно, само по себе наличие заявки не гарантирует выхода на рынок. Между теоретическими ожиданиями и реальной производительностью может существовать большая разница.

Источник: Google patents (US20260003794A1)

Всегда имейте в виду, что редакции могут придерживаться предвзятых взглядов в освещении новостей.

Автор – Sayan Sen